# Silicon Interposer for Millimeter-Wave Heterogenous Integration: Doped vs. High Resistivity Substrates

**CNF Summer Student: Kenta Lin**

Student Affiliation: Ming Hsieh Department of Electrical and Computer Engineering; University of Southern California

Summer Program(s): 2025 Cornell NanoScale Facility Research Experience for Undergraduates (CNF REU) Program

Principal Investigator(s): James C. M. Hwang

Mentor(s): Jin Hong Joo

Primary Source(s) of Research Funding: National Science Foundation under Grant No. NNCI-2025233, SUPREME

Contact: jch263@cornell.edu, kentalin@usc.edu, jj593@cornell.edu Summer Program Website(s): https://cnf.cornell.edu/education/reu

Research Group Website: https://cha.mse.cornell.edu/

Primary CNF Tools Used: SUSS MA6-BA6 Contact Aligner, AJA Sputter Deposition, UNAXIS 770 Deep Silicon Etcher,

PlasmaTherm Versaline System, Veeco Savannah ALD, ReynoldsTech Cu ECD Hood, DC Probe Station, Microwave Small-Signal Probe Station

#### **Abstract:**

As the demand for heterogeneous-integrated RF chips increases, interposers for millimeter-wave circuits using through-silicon vias (TSVs) have become increasingly important due to their low loss and high-power capacity across a wide frequency range. For frequencies above 110 GHz, substrate-integrated waveguides (SIWs) are small enough to be integrated in Si interposers for high-power interconnects.

They can also be used to form high-quality passive devices such as filters and antennas, which have been difficult to integrate on-chip. This enables system-onchip. In this study, we investigate the fabrication of SIWs and grounded coplanar waveguides (GCPWs) in silicon (Si) interposers with a thickness on the order of 200 um with resistivities ranging from 10 to 1 k $\Omega$ ·cm. Thin Si wafers were patterned and etched using the Bosch deep reactive ion etching (DRIE) process to create TSVs. The TSVs are then metallized with platinum (Pt) using atomic layer deposition (ALD) and filled with copper (Cu) using electroplating deposition. DC measurements confirm a TSV series resistance of less than 1  $\Omega$ . Smallsignal millimeter- wave on-wafer measurements show that the coplanar interconnects fabricated on highresistivity (HR, resistivity > 1 k $\Omega$ ·cm) Si have an insertion loss of 0.7 dB/mm at 40 GHz, an order of magnitude better

than the same coplanar interconnects fabricated on doped Si (resistivity < 10  $\Omega$ ·cm).

## **Summary of Research:**

Si is the most extensively used material in semiconductor

devices due to its exceptional electrical and mechanical properties, including a high dielectric constant, electrical resistivity, breakdown strength, and low loss tangent. These characteristics make it an attractive candidate for SIWs. However, its relatively low mechanical toughness and high thermal conductivity compared to materials like silicon carbide (SiC) pose challenges during processing, particularly in etching processes. Our group has previously demonstrated SiC as a viable substrate material for SIW processing. The methodology developed for SiC SIW fabrication is adapted as a proof of principle for Si SIW fabrication.

To develop a processing recipe for Si-based SIWs, we used a thinned HR Si wafer with a thickness of approximately 200  $\mu$ m and resistivity greater than 1 k $\Omega$ ·cm. Building on a similar methodology used for SiC SIWs while leveraging the more mature and faster etching processes available for Si, we began by depositing a 50 nm layer of aluminum oxide (Al2O3) on the wafer's backside using AJA Sputter

Deposition. Al2O3 was selected as the etch mask due to its excellent masking performance in the Bosch DRIE process for Si, providing a high selectivity greater than 1:1000.

The DRIE was performed using either the UNAXIS 770 Deep Silicon Etcher or the PlasmaTherm Versaline System. To ensure effective cooling during etching, the Si wafer was bonded to a sapphire carrier wafer using cool grease. The etching chemistry employed C4F8/SF6, which react with Si to

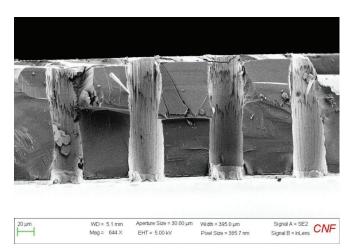

anisotropically form vias. As shown in Figure 1, this process yielded 200 um-deep TSVs with a diameter of 50 um and sidewall angles ranging from 80° to 90°.

Figure 1: Cross-Sectional SEM Images of TSVs.

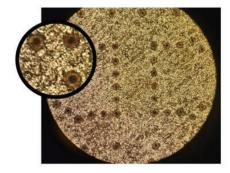

Figure 2: Top-View Optical Image of TSVs After Cu Electroplating.

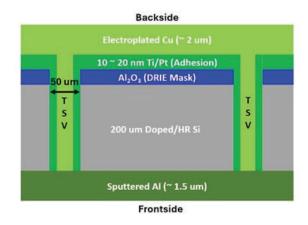

Figure 3: Schematic of Si Interposer Layout.

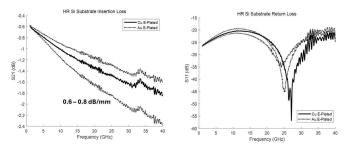

Figure 4: Measured Insertion Loss (S21) and Return Loss (S11) of HR Si Substrate Across 1 – 40 GHz.

After the TSVs were fully etched through, ALD was used to coat the TSV sidewalls with a Pt seed layer. Cu was then electroplated to fill the TSVs, initiating from the Pt seed layer, as illustrated in Figure 2.

Once the backside processing was completed, the front side was patterned with SIW and GCPW lines. A titanium/aluminum (Ti/Al) layer was subsequently deposited using AJA sputter deposition. The structural details and final device configurations are shown in Figure 3.

Both HR and doped Si devices were tested at the High Frequency Test Lab (HFTL) where TSV series resistance and GCPW line performance were evaluated. Using the DC probe station, I-V measurements showed that the TSV series resistance was typically below 1  $\Omega$  for both HR and doped Si substrates. RF

measurements were then conducted over 1 – 40 GHz range using the small-signal probe station, as shown in Figure 4. For HR Si, insertion loss (S21) values ranged from 0.6 to 0.8 dB/mm, with return loss (S11) exceeding 20 dB. In comparison, doped Si devices exhibited insertion loss of approximately 3.2 dB/mm and return loss greater than 10 dB.

### **Conclusions and Future Steps:**

The fabrication of Si interposers focused on optimizing Bosch DRIE of thinned Si wafers and refining metallization processes to achieve uniform anisotropic etching and consistent metal filling across the wafer. Measurements comparing HR and doped Si substrates revealed that HR Si exhibits insertion loss an order of magnitude lower than that of doped Si, highlighting its potential as a promising substrate material for millimeterwave applications. Looking ahead, with updated tools and improved techniques for etching and metallization, fully metal-filled TSVs are expected to achieve insertion losses below 0.5 dB/mm at frequencies up to 220 GHz, utilizing the 220 GHz single-sweep probe station at HFTL.

#### **References:**

- [1] M. J. Asadi, L. Li, K. Nomoto, Y. Tang, W. Zhao, P. Fay, D. Jena, H. G. Xing, and J. C. M. Hwang, "SiC Substrate Integrated Waveguides for High-Power Monolithic Integrated Circuits Above 110 GHz," 2021 IEEE MTT-S Int. Microw. Symp. (IMS), Atlanta, GA, USA, 2021, pp. 669-672.

- [2] D. Malta, E. Vick, S. Goodwin, C. Gregory, M. Lueck, A. Huffman, and D. Temple, "Fabrication of TSV-based silicon interposers," 2010 IEEE International 3D Systems Integration Conference (3DIC), Munich, Germany, 2010, pp. 1–6.

- [3] M. Leskela and M. Ritala, Thin Solid Films 409, 138 (2002).

- [4] F. Laermer et al., IEEE Microelectromech. Syst. 211 (1999).