# **Interconnect-Based Temperature Sensing Array for IC Thermal Management**

**CNF Project Number: 321024**

Principal Investigator(s): Ping-Chuan Wang and Graham Werner

**User(s): Ping-Chuan Wang, Graham Werner**

Affiliation(s): SUNY New Paltz Division of Engineering Programs

Primary Source(s) of Research Funding: SUNY New Paltz Research and Creative Projects Award (RCPA)

Contact: Wangp@newpaltz.edu, Wernerg1@newpaltz.edu Website: https://mcmahon.aep.cornell.edu/index.html

Primary CNF Tools Used: Heidelberg MLA 150, Hamatech Wafer Processor, CVC SC4500 Odd-hour evaporator, YES

EcoClean Asher Filmetrics Reflectometer

### **Abstract:**

Excessive self-heating in integrated circuits (ICs) is a major barrier to performance and reliability within the semiconductor industry and necessitates innovation in thermal management [1,2], prompting detailed measurements of IC temperature with adequate spatial and temporal resolutions in designing and characterizing innovative cooling devices. This project presents the fabrication of an in-line spatial and temporal temperature mapping system designed to interface directly between an IC and its cooling device, consisting of a dense array of 64 aluminum Resistance Temperature Detector (RTD) sensors. The RTD array was successfully fabricated at CNF using a single-layer lift-off process on an oxide-coated silicon wafer, before integration into a measurement system. Our project validates the design, fabrication, and characterization of an aluminum RTD sensor array system for in-situ, high resolution thermal mapping, contributing to the experimental evaluation of IC thermal management solutions.

## **Summary of Research:**

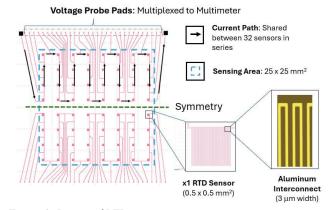

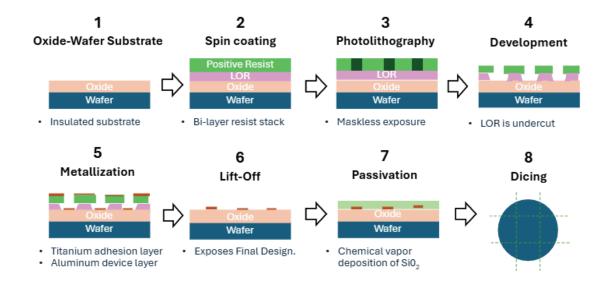

Resistance Temperature Detectors (RTDs) were chosen due to their straightforward device physics, use of a single conventional conductor, and fabrication simplicity through a single lithography step [3,4]. The RTD structure consisted of 64 individual serpentine-pattern sensors, spaced evenly to cover a 25 mm x 25 mm sensing area (Figure 1), with two arrays fabricated on a single 4-inch wafer. Fabrication employed a lift-off process on silicon wafers first passivated with thermally grown SiO2 (Figure 2). A bi-layer of lift-off resist and positive tone photoresist were spin-coated before pattern development. The Heidelberg MLA 150 maskless direct-write tool was used to expose the RTD design. The exposed photoresist was then developed in a Hamatech-Steag wafer processor, followed by dry-

oxygen plasma descum using an Anatech plasma asher to remove resist residues.

Following development, metallization was performed, where A 100 Å titanium adhesion layer was followed by deposition of 2000 Å of aluminum using electron beam physical vapor deposition (EB-PVD). Lift-off was performed with an automated tool, and SiO2 passivation was applied atop metal pattern using PECVD after optimizing pre-cleaning to avoid damage to the aluminum, providing necessary electrical and mechanical insulation. After dicing and packaging, the calibrated system performed real-time measurements by multiplexing continuously across the sensor array to perform 4-point resistance measurements.

Once calibrated, the sensor array showed minimal sensor-to-sensor temperature variation under ambient conditions, with 0.18% variability at room temperature. During thermal transients, spatial temperature variations were resolved within 0.1 °C.

# **Conclusions and Future Steps:**

The fabricated RTD sensor array successfully demonstrated ambient and transients with suitable spatiotemporal resolution for non-uniform thermal gradients during heating and cooling cycles. The measured average sensitivity was  $0.197 \pm 0.004$  mV/°C, consistent with design expectations. Limitations include aluminum's inferior thermal properties compared to platinum for RTDs, and a lower spatial resolution of 10 sensors/ cm², which may be insufficient in some applications. Future work will focus on validating the system through numerical modelling or thermal finite element analysis (FEA) to ensure accuracy in detecting spatial temperature variations.

### **References:**

- [1] International Technology Roadmap for Semiconductors 2.0, 2015 ed., Executive Report (https://www.semiconductors.org/wp-content/uploads/2018/06/0\_2015-ITRS-2.0-Executive-Report-1.pdf, accessed May 8, 2025)

- [2] L. Shang and R. P. Dick, "Thermal Crisis: Challenges and Potential Solutions," IEEE Potentials, vol. 25, no. 5, pp. 31-35, (2006) (doi: 10.1109/MP.2006.1692283)

- [3] G. Werner, "Development of IC-based Temperature Monitor with Spaciotemporal Resolution," M.S. thesis, State University of New York at New Paltz, 2025.

- [4] G. Werner, P.-C. Wang, O. Trzcinski, and W. Cui, "Interconnect-Based Sensor Array for Characterizing Thermal Management of IC Chips," 2025 TMS Annual Meeting, Las Vegas, NV, March 2025

Figure 1: Layout of RTD sensor array.

Figure 2: Lift-off fabrication steps.