# Fabrication of Non-Volatile Memory Transistors Using Hybrid Two-Dimensional Materials

## CNF Project Number: 3064-23 Principal Investigator(s): Yu Zhong User(s): Haolei Zhou, Qiyi Fang, Kaushik Chivukula, Ashutosh Garudapalli

Affiliation(s): Department of Materials Science and Engineering, Cornell University Primary Source(s) of Research Funding: Cornell Startup Funding Contact: yz2833@cornell.edu, hz595@cornell.edu, qf52@cornell.edu, kc836@cornell.edu, ag2289@cornell.edu Research Group Website: https://zhong.mse.cornell.edu/ Primary CNF Tools Used: Oxford 100 PECVD, DWL 2000 Mask Writer, DWL 66FS Writer, Odd Hour Evaporator, Even Hour Evaporator, ABM Contact Aligner

### **Abstract:**

This project is focused on the fabrication electrolyte-gated of nonvolatile memory transistors based on hybrid two-dimensional (2D) materials. The goal is to understand how the hysteresis changes under various measurement conditions for a memory transistor made from a hybrid MoS<sub>2</sub>-crow ether thin film. The retainability of ions inside the film is the main factor of such a hysteresis phenomenon. Previous research

shows that the  $MoS_2$ -based transistors may have a small hysteresis at high gate voltage or due to factors such as high moisture absorption [1]. In our experiment, we used liquid electrolytes instead of typical solid-state electrolytes. By applying this change, we found a much lower turn-on voltage and a much larger hysteresis. In addition, by adding a thin layer of a 2D crown ether polymer (CEP) film on top of monolayer  $MoS_2$ , the retention time of ions seems to increase and hence increases the hysteresis. Such hysteresis is critical for neuromorphic computing such as potentiation or depression.

### Summary of the Research:

To synthesize CEP films, we used a method called laminar assembly polymerization in a homemade Teflon reactor [2]. The CEP films were grown at the interface between water and pentane. In the bottom of the reactor, 2,4,6-trihydroxybenzene-1,3,5-tricarbaldehyde was dissolved in deionized water. For the injected solution, 6,7,9,10,17,18,20,21-octahydrodibenzo[b,k]

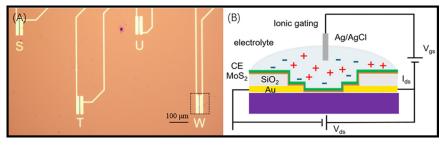

Figure 1: (A) Optical image of fabricated FET device covered with  $MoS_2$  single layer film and (B) Schematic of the memory transistor.

[1,4,7,10,13,16]hexaoxacyclooctadecine-2,13-diamine dissolved in a solution of mixed chloroform and methanol with a ratio of 3:1 was delivered through the top pentane phase. By gradually injecting the solution, the CEP film was formed at the interface.

For the device fabrication, a set of lithographic tools at Cornell NanoScale Facility was used. Figure 1 shows an optical image and schematic of the device. To make the device, a contact alignment mask was first made. The patterns of masks were tested via DWL 66FS writer. There are two masks made by DWL 2000 mask writer. The first mask is for defining the metal contacts. the basic structure of the device with a channel length of 150 micrometers and a channel width of 10 micrometers.

A 280 nm silicon dioxide is deposited on the p-doped pure silicon by the plasma-enhanced chemical vapor deposition. Then S1813 was spin-coated on the substrate with a recipe of 5000 rpm – 40s. ABM contact aligner is then used for exposing the photoresist. MIF-726 60s recipe was applied to develop the photoresist. The deposition of a 10 nm Ti/ 100 nm Au electrode was accomplished by the odd-hour evaporator with a ratio of

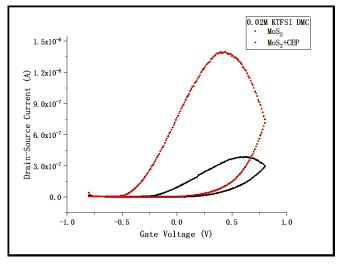

*Figure 2: Transfer curve of MoS2 devices with (red) and without CEP film (black).*

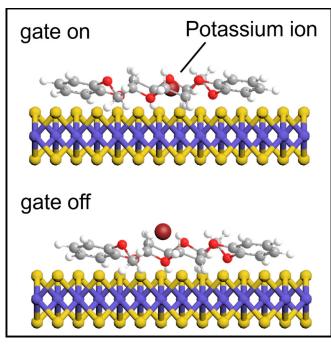

Figure 3: Schematic of memory effect from a MoS2-CEP film.

one angstrom per second at a power of approximately 10%. The liftoff process was done with 20 minutes of S1165 remover, 20 minutes of acetone and five minutes of isopropanol. The second mask is designed for the insulating layer. The same processes were done except for the deposition part. 80nm of silicon oxide was deposited on the device with the even-hour evaporator. The rate was approximately 3.5 angstrom per second at a power of 3%.

To complete the device fabrication, we first transferred MoS2 on the prepatterned electrode mentioned above followed by transferring the CEP film on MoS2. We compared the transfer curve of MoS2 transistors with and without CEP film. The device with a CEP film shows a more significant hysteresis than that without a CEP film (Figure 2). Our hypothesis is that the presence of CEP film can increase the retention time of ions on the MoS2 surface due to the strong interaction between the cations and crown ether units (Figure 3). Further investigations are underway to reveal the mechanisms for the memory effect.

#### **Conclusions and Future Plans:**

The MoS2 device exists some hysteresis intrinsically in the liquid electrolyte. Such hysteresis is closely correlated with the concentration of the liquid electrolyte and the dielectric constant of the solvent. The addition of CEP film will increase the retainability of ions on the films because of strong cation-crown ether interactions. In the future, a device with better performance (lower channel width) can be designed to reduce the effect of the leakage current.

#### **References:**

- [1] Late, D. J.; Liu, B.; Matte, H. S. S. R.; Dravid, V. P.; Rao, C. N. R., Acs Nano 2012, 6 (6), 5635-5641.

- [2] Zhong, Y.; Cheng, B.; Park, C.; Ray, A.; Brown, S.; Mujid, F.; Lee, J.-U.; Zhou, H.; Suh, J.; Lee, K.-H.; Mannix, A. J.; Kang, K.; Sibener, S. J.; Muller, D. A.; Park, J. Science 2019, 366 (6471), 1379-1384.